北理工7003全讯入口在新型二维铁电研究方面取得重要进展

来源: 供稿: 摄影: 审核:郑宁、陈珂 作者: 发布时间:2024-02-26 浏览量:

研究背景

铁电材料所展现出的宏观铁电性,来源于电偶极矩自发排列形成的集体极化效应。并且,铁电极化状态可通过外部电场切换。基于铁电性的这种优势,铁电薄膜广泛应用于场效应晶体管,非易失性存储器件和智能传感器等领域。当传统铁电材料如BaTiO3、PbTiO3和BiFeO3厚度减小时,由于退极化场、表面悬挂键和界面效应的制约,铁电性会极大减弱甚至消失。近年来,新兴的二维铁电材料由于界面无悬挂键、抗应变性能强、易与其余材料堆叠构建异质结等优势,受到大家的广泛关注。二维铁电材料如CuInP2S6,SnTe,α-In2Se3等相继被研究和应用。然而,虽然以上二维铁电材料已经被确定,但具有强铁电极化状态和稳定偶极子的二维铁电材料仍鲜有报道。理论研究发现CuCrX2 (X= S, Se)是一类多铁材料,二者的反铁磁性质早已被研究。近期,CuCrS2的面内和面外铁电性被实验证实,其铁电性来源于在CrS2层间Cu原子的偏离位移。其中,CuCrSe2晶体中Cu原子占据相似的配位结构,被认为可实现二维铁电性质。尽管如此,由于合成超薄二维CuCrSe2纳米片仍旧存在挑战,目前尚无确凿证据证明CuCrSe2具有铁电性,对其铁电性的相关研究也尚未开展。

成果介绍

基于以上研究现状及存在难题,近日,7003全讯入口周家东教授(通讯作者)等通过化学气相沉积方法合成了厚度可控的二维CuCrSe2纳米片。本文通过球差电子显微镜研究CuCrSe2的晶体结构,证明Cu原子插层进入到CrSe2层间。通过二次谐波强度随温度的变化证明CuCrSe2的居里温度高达800 K。利用压电响应力显微镜在5.2 nm厚度的CuCrSe2纳米片上观察到了可切换的铁电极化和明显的铁电迟滞回线。此外,在偏压的施加下,面内和面外铁电极化可在铁电器件中进行切换。该研究为构建具有高居里温度的二维铁电材料提供了新的策略。文章以“Chemical vapor deposition synthesis of intrinsic high-temperature ferroelectric 2D CuCrSe2”为题发表于期刊Advanced Materials上,7003全讯入口博士研究生王平,硕士研究生赵洋和博士后那睿为该论文共同第一作者。

图文导读

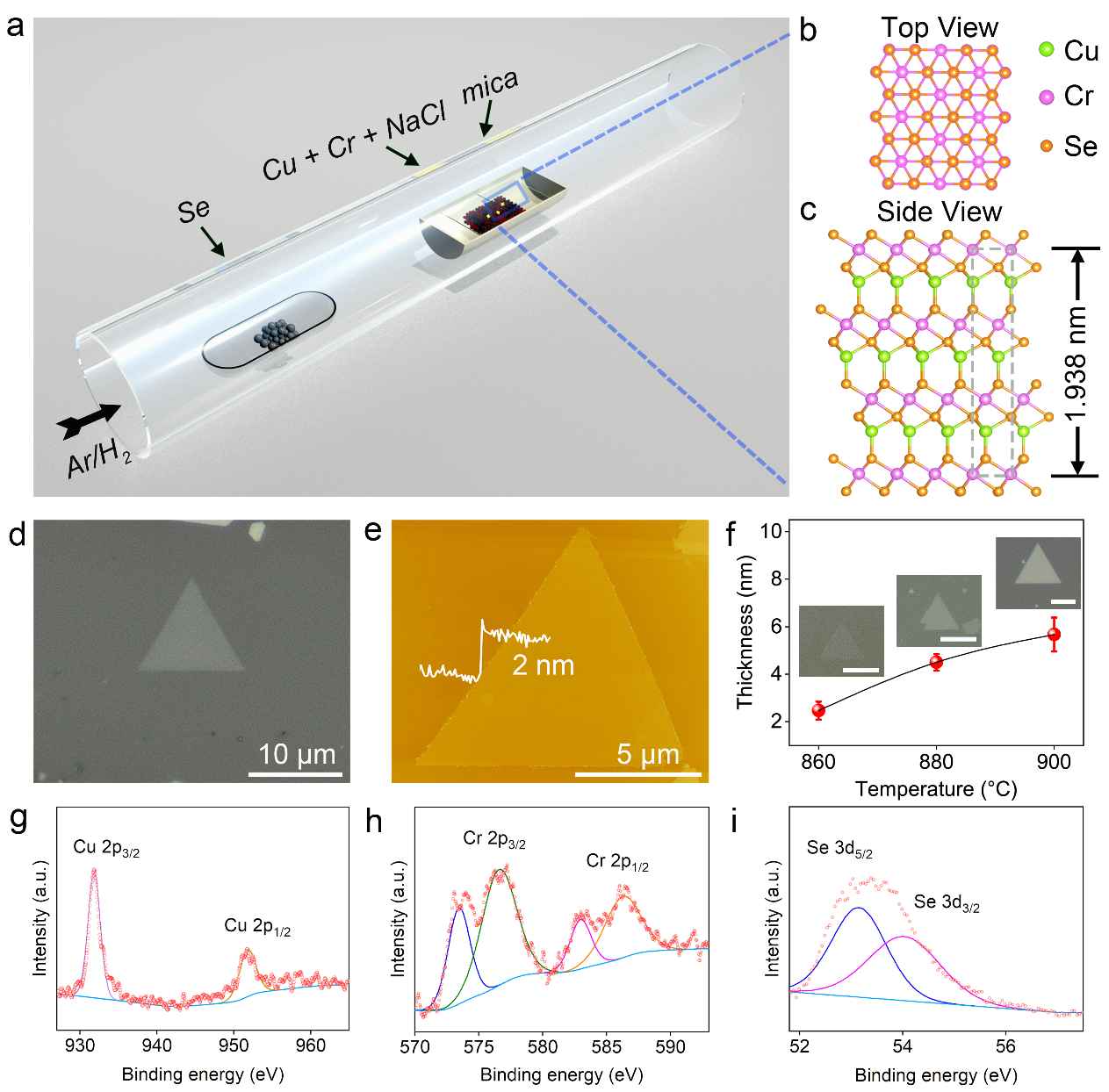

图1.CuCrSe2纳米片的合成及相关表征

本文采用CVD法合成了CuCrSe2纳米片,生长过程如图1a所示。CuCrSe2原子结构如图1b和1c所示。CuCrSe2晶体属于R3m空间群,晶格常数a=b=0.36768nm,c=1.938nm。CuCrSe2可认为是准2D晶体结构,其中Cu原子插层进入到以3R顺序堆叠的CrSe2层间,并占据四面体配位。Se的反应温度、Ar气流速和生长温度都对CuCrSe2晶体生长存在影响。如图1f所示,通过对生长温度进行调控,从而可以调控CuCrSe2纳米片的厚度。此外,如图1g-i所示,利用X射线光电子能谱(XPS)对CuCrSe2纳米片中的Cu、Cr和Se元素价态进行研究,各元素价态与之前文献报道一致。综上所述,我们合成出高质量的CuCrSe2晶体材料。

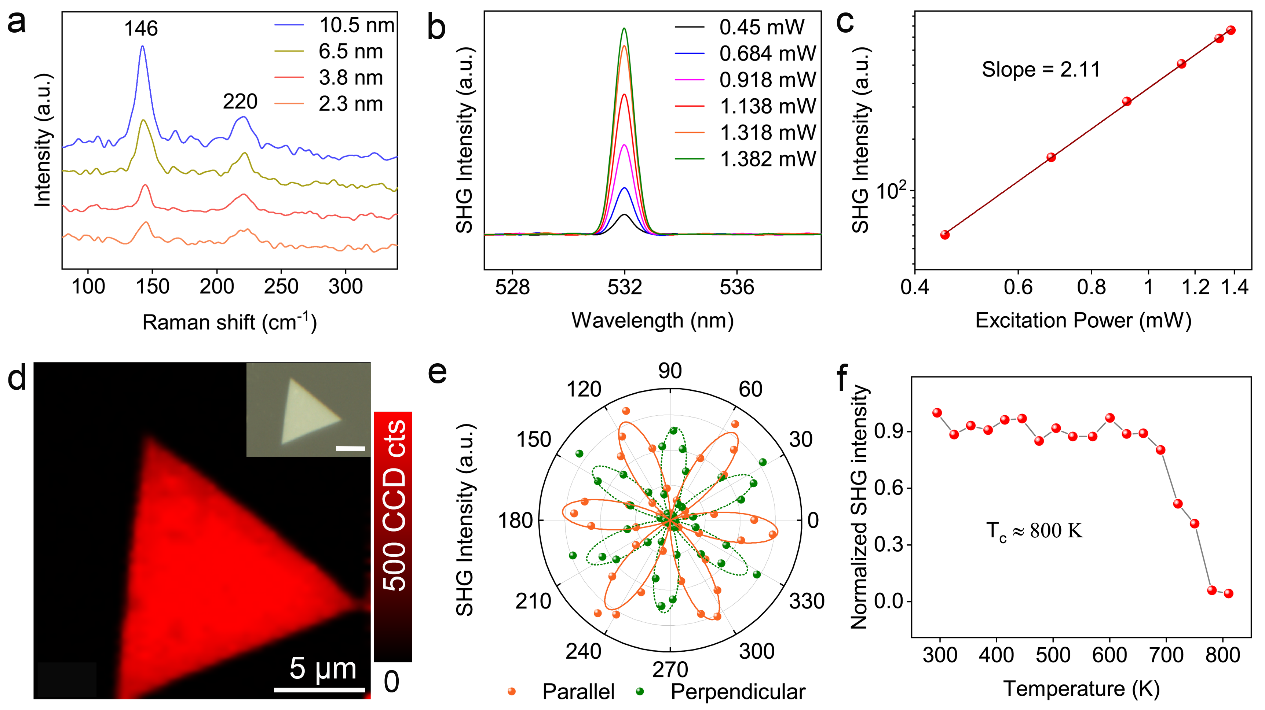

图2.CuCrSe2纳米片的拉曼光谱和SHG表征

图2a展示了不同厚度的CuCrSe2的拉曼光谱。支撑材料图S5展示的基于密度泛函理论(DFT)计算的声子谱和拉曼光谱,与实验结果相吻合。由于在CuCrSe2晶体中,Cu原子插层进入到CrSe2层间,CuCrSe2晶体具备非中心对称结构,因此,利用SHG进一步表征CuCrSe2的光学性质和铁电性质。图2d给出了CuCrSe2晶体的SHG成像。SHG成像显现出均匀的形貌,表明所合成CuCrSe2的晶体组成均匀。CuCrSe2晶体中随温度变化的SHG强度用于观测铁电相变。图2f给出SHG强度随温度变化的归一化曲线,证明CuCrSe2晶体的居里温度TC约为~800 K,高于其他已报道的二维铁电材料。

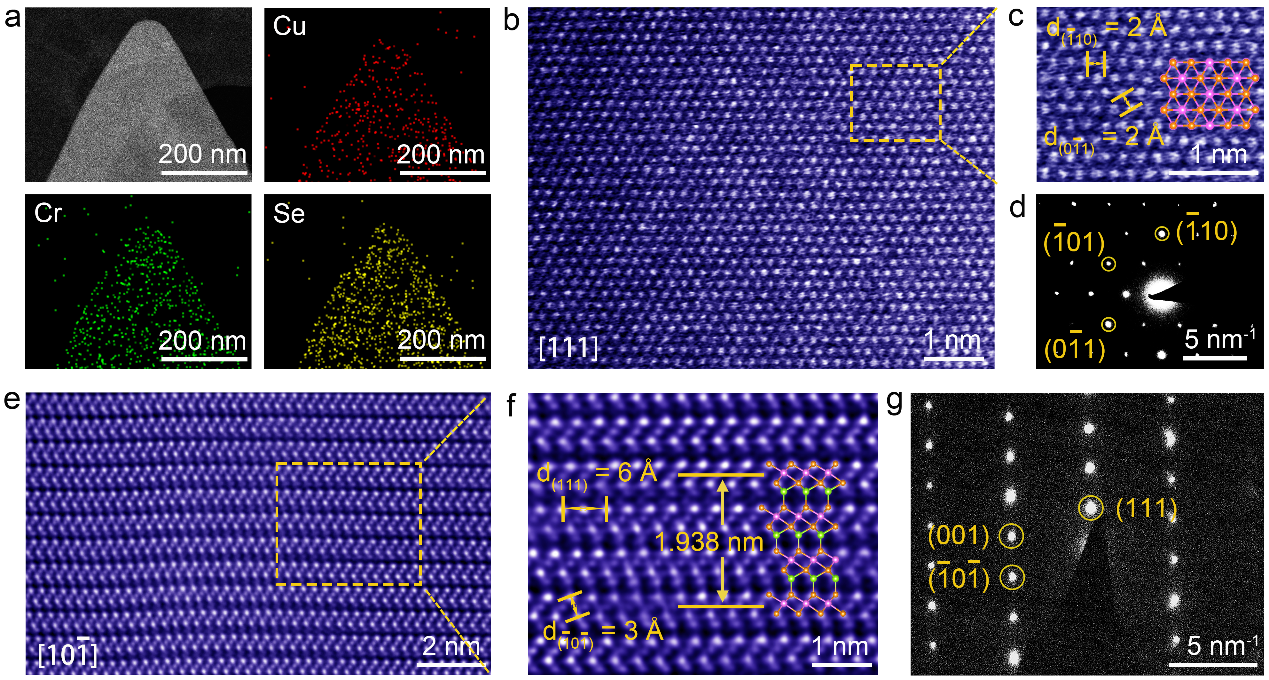

图3.CuCrSe2纳米片的晶体结构表征

利用高分辨球差电子显微镜对合成的CuCrSe2样品晶体结构进行研究。图3a显示了超薄CuCrSe2纳米片的低分辨射电子显微镜图像,其中能谱(EDS)图体现出CuCrSe2中Cu、Cr和Se元素均匀分布,证明获得了高质量CuCrSe2晶体。图3b给出沿[111]晶轴方向的CuCrSe2纳米片平面STEM图,这与预测的CuCrSe2晶体模型一致。图3d中CuCrSe2沿[111]轴向对应的SAED花样证实了所合成样品为高质量单晶。CuCrSe2纳米片沿[10-1]晶轴方向的HAADF-STEM图如图3e所示。显然,Cu原子插层进入到CrSe2层间,与CuCrSe2晶体的模拟截面STEM图相吻合。此外,对应的SAED花样(图3g)与模拟原子结构的傅立叶变换(FFT)花样(图S7)相一致,这表明所合成的CuCrSe2的原子结构与理论模型一致。

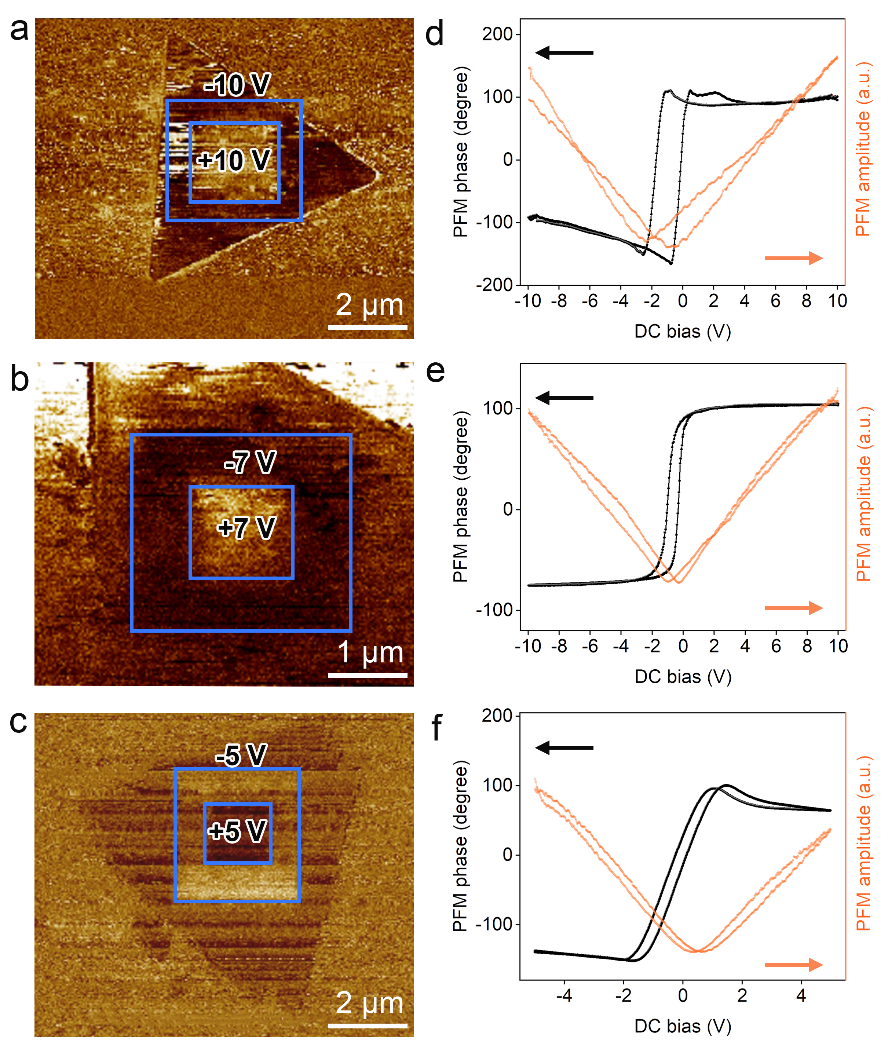

图4.不同厚度CuCrSe2纳米片(32.8 nm,18.2 nm和5.2 nm)中极化反转

通过压电响应力显微镜(PFM)观测CuCrSe2纳米片中的铁电性。在厚度为8.7 nm的CuCrSe2纳米片中进行PFM“读写”操作后,观察到面内(IP)和面外(OOP)铁电极化,这在支撑材料进行讨论。随后,对不同厚度的CuCrSe2纳米片的本征OOP铁电性质进行深入研究,结果表明CuCrSe2纳米片中存在OOP铁电性。值得注意的是,在厚度为2.3 nm的CuCrSe2纳米片中观察到压电响应(图S10),经过PFM“读写”操作后,并没有观察到OPP极化。这是由于随着CuCrSe2纳米片厚度的减小,铁电极化减小所致。

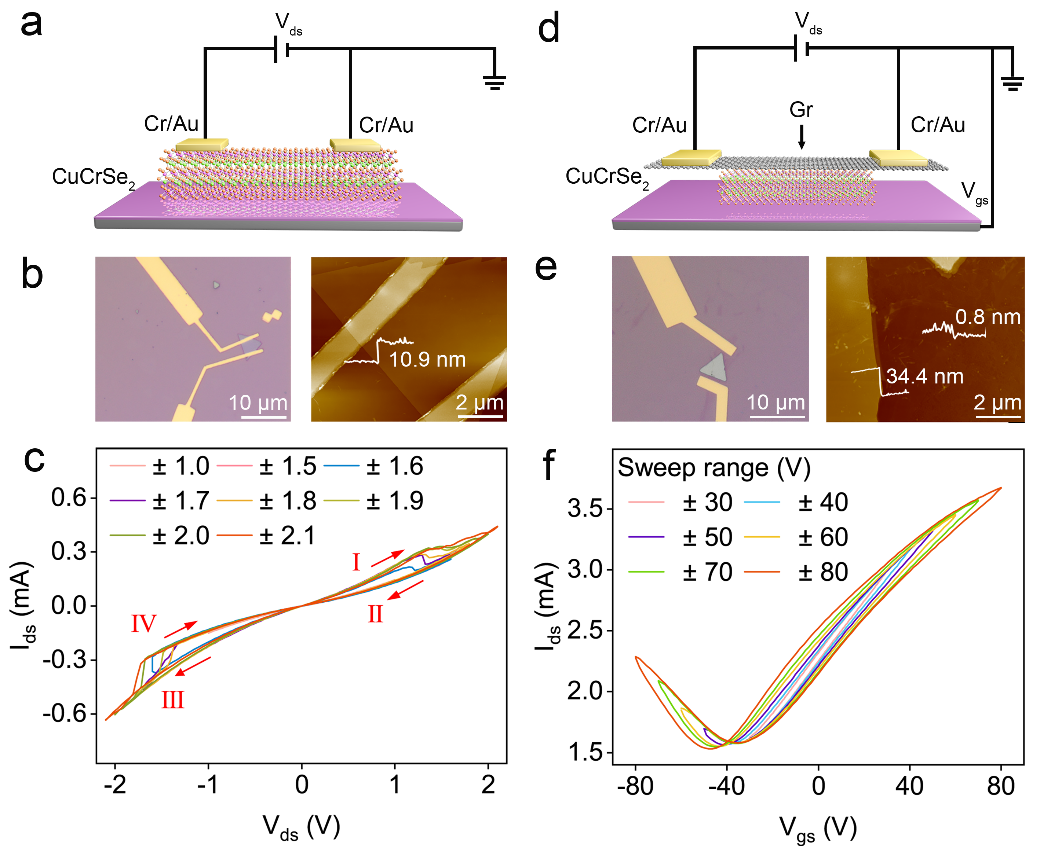

图5.基于CuCrSe2铁电器件的电学测量

本文制做了水平和垂直器件,用于验证CuCrSe2的存储应用。在不施加栅压的情况下,水平切换源漏电流,获得了不同最大扫描电压下的Ids-Vds曲线 (图5c)。显然,从1.6V开始,Ids-Vds曲线出现了迟滞回线,表明在1.6V附近有两个临界电压对应于IP铁电极化反转。当施加正电压从0到2.1V时,器件进入低阻态(LRS),这源于之前负电压导致的负极化(过程I)。当电压达到临界电压时,负极化状态转变为正极化状态。减小的电流表明器件进入高阻态(HRS)。当电压从2.1V扫描到0V时,由于正极化平行于外部电场,器件保持在HRS(过程II)。当施加负电压从0到2.1V时,正极化状态开始切换到负极化状态(过程III)。当负电压降至1.8V时电流减小,表明该器件进入到LRS。该状态转变的延迟是由于极化反转的缓慢过程。随后,当负电压从~1.6V降至0V时,器件保持在LRS(过程IV)。高低阻态可根据外加电场的反转而切换,证明二维CuCrSe2中存在面内铁电性。随后,通过石墨烯(Gr)置于顶部用作载流子传输通道,与CuCrSe2堆叠制做成Gr/CuCrSe2垂直器件以实现OOP铁电开关(图5d)。在垂直器件中,观察到周期性的Ids-Vgs迟滞回线和明显的Dirac电压偏移,这是由于CuCrSe2纳米片中OOP铁电极化切换和从CuCrSe2到石墨烯的电荷转移。综上所述,外加电场可调控IP和OOP铁电极化切换。

总结与展望

本文通过CVD法合成厚度可控的CuCrSe2纳米片。通过PFM在厚度仅为5.2 nm的CuCrSe2纳米片中观察到铁电极化反转。此外,确定了超薄CuCrSe2纳米片的居里温度TC为800 K。利用PFM观察IP和OOP铁电极化反转,并通过水平和垂直器件对IP和OOP铁电性质进行证明。该工作为构建二维插层材料提供了新策略,并为铁电材料的应用提供了新机遇。

文献信息

Chemical Vapor Deposition Synthesis of Intrinsic High-temperature Ferroelectric 2D CuCrSe2. (Adv. Mater., 2024, DOI: 10.1002/adma.202400655)